The CPU Multicore Bottleneck: Solving it With Internet-Style Networks

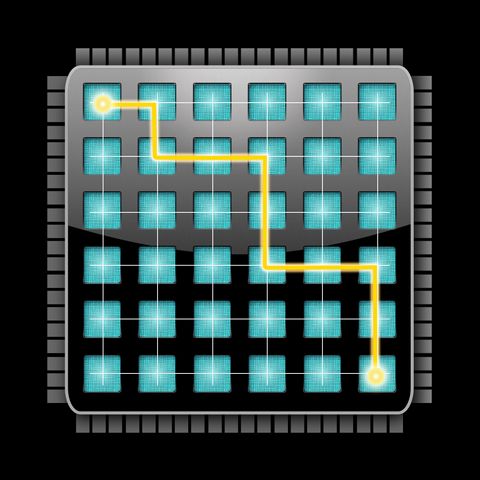

As CPU core count goes up, communications between the cores begin to hit significant bottlenecks. This is because these cores are still using the decades old data bus model of transferring data between each other, which prevents multiple simultaneous communications and is because it only works between two cores at a time. To get over this, researcher Li-Shiuan Peh at MIT is looking to use internet-style packet-switched networks right within the CPU itself. The idea is to replace the long wires of the traditional data bus with much shorter ones connecting one core to another and using a router on each core to arbitrate the data exchange between cores. This work is still very much in the research phase however, so don’t expect any products based on this technology anytime soon. This approach isn’t all that surprising when one considers that the PCI Express bus uses a network-style connection model. This intra-core communication model is fascinating and it’s well worth reading the detailed explanation at the link below.

In an on-chip network, however, a packet of data traveling from one core to another has to stop at every router in between. Moreover, if two packets arrive at a router at the same time, one of them has to be stored in memory while the router handles the other. Many engineers, Peh says, worry that these added requirements will introduce enough delays and computational complexity to offset the advantages of packet switching. “The biggest problem, I think, is that in industry right now, people dont know how to build these networks, because it has been buses for decades,” Peh says.

Comments are closed.