AMD Marketing Slides At Hot Chips Show Off Bulldozer CPU Architecture

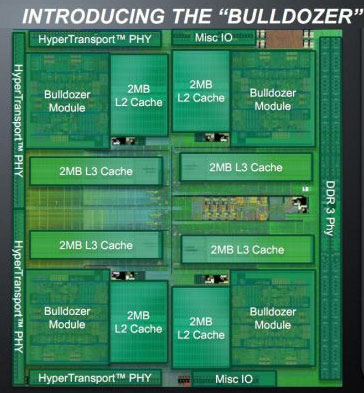

At this year’s Hot Chips in California, AMD has shown detailed information about the architecture of the companies next generation bulldozer processors. The company also had a Zambezi-FX CPU in a system at Gamescom 2011, so it looks like Bulldozer is getting closer to hitting the streets now that they are being shown to the public and in good working order. The slides posted on technic3d show the Bulldozer CPU die diagram, power saving and Turbo Core 2.0 features. The Zambezi-FX Processors detailed by AMD in the slides was a FX-8150 CPU.

AMD shows the architecture of the example of a Zambezi samples with model number FX-8150th The processor consists of four modules, bulldozers, comprising of two integer cores plus floating point core. The floating point core can work either as a 256 bit unit, two 128-bit or edit commands, so the bulldozer thus supports the new AVX instructions. Each module stands 2MB L2 cache and 32KB L1 cache. FX-8150, four such modules connected via the Northbridge along with 8MB L3 cache and two 72 bit channels are connected to the memory. The 72 bits come with 64-bit data lines and 8-bit error correction together.

Comments are closed.