AMD Discusses Fusion ‘Llano’ Processors at ISSCC

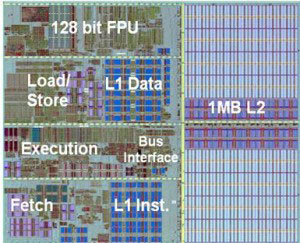

Yesterday afternoon at ISSCC in San Francisco, AMD presented details on the forthcoming 32nm Fusion APU slated for 2011, codenamed Llano. AMD Senior Fellow, Samuel Naffziger, walked attendees through several power management innovations to the x86 core, which he has also detailed in this blog post. The blog post confirms that the Fusion processor will feature four CPU cores, DDR3 memory and a DirectX 11 capable SIMD engine integrated on-die. The Fusion processor will be the first AMD CPU to use 32nm SOI processor technology when it launches in 2011. This accelerated processing unit (APU )is expected to first appear within the forthcoming Sabine platform for mainstream notebooks. And just to show how real it all is, the picture below shows the cores more than 35 million transistors that fit within 9.69mm2 (not counting the 1MB of L2 cache shown on the right):

At AMD, we live by the mantra that the Future is Fusion and our global engineering teams are working aggressively to deliver the industrys first accelerated processing unit (APU) in support of it. That said, the consumer trends that led AMD to embark toward developing APUs began years ago; the idea wasnt born in either a CPU or a GPU, but was born in how consumers began using their PCs. Things like: streaming video, immersive gaming, 3D user interfaces, enhanced multimedia and other compute intensive tasks became the norm rather than the exception. As an engineer, my job is to help figure out how the nuts and bolts can best fit together to help improve the users experience; our team is presenting today at the International Solid State Circuits Conference (ISSCC) in San Francisco some of the results of those efforts.

Comments are closed.